Vol.43 No.1 Mar. 2023

技术与测试

DOI:10.19453/j.cnki.1005-488x.2023.01.014

# 基于混合波束赋形架构的数字中频系统 方案设计

毕鹏1\*,周骏2,包宽2

(1. 南京电子器件研究所,南京 210016; 2. 南京国博电子股份有限公司,南京 211111)

摘 要:对基于混合波束赋形的系统架构进行了研究。提出了新型的混合波束赋形架构,并采用高集成宽带收发芯片AD9361与全可编程片上系统进行多通道数字中频系统的搭建。测试结果表明该方案稳定可靠,满足大带宽高速传输的需求。

关键词:混合波束赋形;宽带收发芯片;全可编程片上系统

中图分类号: TN929.5 文献标志码: A 文章编号: 1005-488X(2023)01-0085-05

# Design of Digital IF System Based on Hybrid Beam Forming Architecture

BI Peng, ZHOU Jun, BAO Kuan

- (1. Nanjing Electronic Devices Institute, Nanjing 210016;

- 2. Nanjing Guobo Electronics Co., LTD, Nanjing 211111)

**Abstract:** The system architecture based on hybrid beam forming was studied, a new hybrid beam forming architecture was proposed, and highly integrated broadband transceiver chip AD9361 and all programmable SoC was used to build a multi-channel digital intermediate frequency system. The test results showed that the scheme was stable and reliable, and could meet the demands of large bandwidth and high speed transmission.

**Key words:** hybrid beam forming; broadband transceiver chip; all programmable SoC

#### 引言

随着新一代通信技术的推进,5G 网络针对连接密度、通信速率和延时性提出了较大的提升要求。为了满足5G 网络爆炸性数据增长和巨大的连接密度,需要在通信系统和传输技术上进行研究和提升。由香农定理可知,提升系统容量主要有三个

方向:1)增加带宽;目前低频段频谱资源难以满足5G的大带宽需求,5G的潜力在毫米波高频段。2)增加网络覆盖;通过超密集组网的方式可以充分利用频谱资源,但是也对通信设备提出了低功耗、小型化的要求。3)提升频谱效率;高阶调制技术和复用技术是4G网络提升频谱效率的有效手段,但是5G获得较大频谱效率提升的关键在于波束赋形技

收稿日期:2023-02-05

**作者简介:**毕 鹏(1999—),男,硕士研究生,主要研究方向:混合波束赋形技术,嵌入式系统;(Email:3014473228@qq. com)

包 宽(1987—),男,博士,高级工程师,主要研究方向:微波毫米波射频前端领域新技术以及新应用研究;

周 骏(1982一),男,博士,研究员级高工,主要研究方向:毫米波高密度集成与射频微系统技术。

<sup>\*</sup> 通讯作者

术结合大规模天线技术。传统网络中,天线尺寸较大而天线数量较小,往往采用每个天线都通过单独的射频链路连接到基带处理单元,即采用数字波束赋形的方式获得较高的增益以及优越的波束灵活性。但是对于大规模天线网络,数字的架构不仅在复杂度上难以接受,基带的数据处理单元也很难同时处理大量通道数据。而模拟波束赋形在架构上简单,但是在灵活性和性能上都有较大损失。由此,设计基于混合波束赋形的硬件方案,保留系统灵活性的同时具有较低的系统复杂度,采用ADI宽带收发芯片AD9361设计多通道射频链路,并采用ZYNQ全可编程片上系统实现数字信号处理单元。

## 1 方案设计

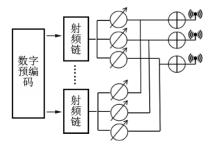

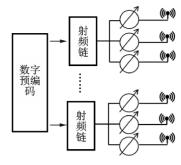

混合波束赋形作为数字波束赋形和模拟波束赋 形的结合,在基带进行低维数字预编码的同时在射 频进行高维模拟预编码,两者的结合有效的降低了 系统硬件设计的复杂度,同时还保证了一定的灵活 性。混合波束赋形根据数字通道与射频通道之间的 连接关系可分为全连接架构和部分连接架构[2]。如 图 1 所示,在全连接架构中,单个天线与所有的数字 通道都建立了连接关系,这种情况下,模拟波束控制 部分较为灵活,可对波束进行较好的优化处理,整个 系统的性能接近数字波束赋形。但该方案在前端需 要使用大量的功分器和加法电路,在大规模阵列中, 不仅硬件复杂度增加,同时也会带来插入损耗的增 大,反而导致系统性能降低。图2为部分连接架构, 单条数字通道通过独立的射频链与一个子阵上的天 线连接,大大降低了硬件复杂度,同时对数据处理速 度和容量的需求也大大降低。

图1 混合波束全连接架构

Fig.1 Hybrid beam fully connected architecture

基于此提出混合波束赋形新型架构,采用部分连接的形式,在降低复杂度的同时保证系统的灵活性,实现针对多用户数据流的分离,提高了系统的频谱效率并降低了整个系统的体积和功耗。射频前端共有64个天线单元,形成8×8矩形天线阵,将天线阵以2×8的形式划分为4个子阵,分别连接4个独

图 2 混合波束部分连接架构

Fig.2 Partial connected architecture of hybrid beam

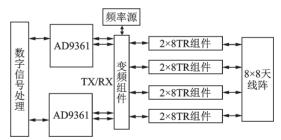

立的数字通道,子阵每个天线使用单独的T/R通道,通过T/R组件内的移相模块和衰减模块完成模拟域的波束赋形,通过横向的子阵划分方式使得阵列采用多波束服务多个用户时波束横向的扫描能力大大提高,提升波束的覆盖能力。对射频链路方案,考虑通信系统低复杂、小型化、大带宽、低功耗以及可拓展的要求,设计采用宽带射频捷变收发器AD9361,其发射与接收的带宽可达56 MHz,考虑到系统传输滚降,可满足系统方案40 MHz带宽的需求。单片AD9361支持两发两收,本方案设计采用全可编程片上系统ZYNQ-7000实现数字信号处理,通过AD9361实现传输链路,完成由基带数据流向中频信号的转化,并通过变频组件将信号搬移至毫米波频段,实现大带宽毫米波信号的发射和接收。

图 3 基于AD9361的混合波束赋形架构

Fig.3 Hybrid beam forming architecture based on AD9361

相较于模拟波束系统,多个数字通道的设计使得系统可同时实现多用户的数据传输,通过波束控制,最多可支持4个用户的同时传输,大大提高了系统的频谱效率和灵活性。但同时射频通道数量远少于全数字系统,硬件复杂度上大大降低。同时采用集成化收发芯片代替传统链路设计,设计周期大大缩短。

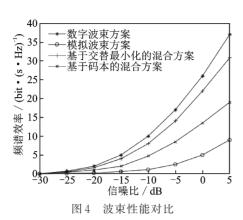

混合波東赋形架构的主要原理是将天线阵子的幅相控制分为数字部分和模拟部分,进行两个矩阵的预编码,目前已有较多的研究[3-6]。文献[3]中提出了一种基于交替最小化的迭代预编码算法,可以获得较好的性能,但算法设计复杂,迭代次数大。文献

[4]中提出了一种基于码本的混合波束预编码方案, 虽然在性能上有所损失,但算法复杂度大大降低。

Fig.4 Beam performance comparison

图 4 所示为两种算法在文中方案下的仿真分析。可以看出,基于交替最小化的算法性能接近数字波束,基于码本的算法性能损失则较大,但基于码本的算法在波束切换速度上远快于其他算法。考虑到毫米波基站覆盖范围较小,用户短距离的移动会导致较大的角度偏移,选取复杂度较低的预编码算法是较好的选择。

# 2 宽带收发数字中频设计

#### 2.1 数字中频方案设计

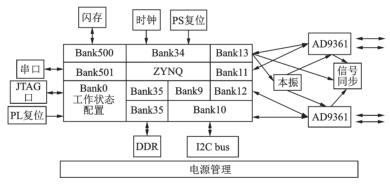

文中设计数字中频方案,数字信号处理部分采 用ZYNQ实现,ZYNQ芯片在架构上与传统FPGA 不同,在包含可编程逻辑资源(PL侧)的同时,还搭 载双核 ARM 芯片(PS侧)。集成的设计方式不仅大 大减小所占空间,而且使得ARM与FPGA之间的 通信速率大大提高,外设接口的配置也更加灵活。 在PL侧设计高性能数字处理算法,PS侧实现外部 接口的驱动以及内部功能的控制。设计ZYNQ通 过 SPI 的方式与 AD9361 实现控制数据的通信,其 SPI接口挂载于PS侧AXI4 Lite总线上,实现小规 模数据的传输,通过6位LVDS信号与单片AD9361 实现信号数据的传输。LVDS接口挂载于 AXI4\_Stream 总线,实现数据流的传输,满足大量高 速数据的传输,同时采用单独的晶振提供信号载波 的时钟,保证其稳定性。如图5所示,系统设计将 数字部分和AD9361芯片集成为四通道收发数字中 频模块,集成化的设计大大减小了空间占用,同时 也增强了系统的可靠性。其原理框图如图5所示。

图 5 数字中频原理框图

Fig.5 Digital IF block diagram

宽带收发系统数字中频设计,发射通道和接收通 道均工作在2.6 GHz附近,系统采用频分复用FDD 的模式,通过ZYNQ对AD9361控制寄存器进行写入 来实现波束数字域的控制。设计指标如表1所示:

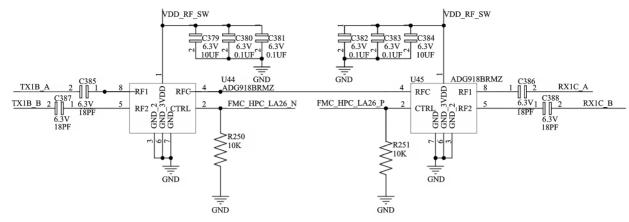

#### 2.2 信号同步设计

本方案设计中采用两片 AD9361,但是芯片不支持多片的同步控制,需在外部增加同步电路进行控制。采用两片 ADG918BRMZ分别对发射信号和接收信号进行采样,并与 ZYNQ连接通过设定的程序进行同步处理。发射和接收的同步控制电路如图 6 所示。

表 1 数字中频系统设计指标

Tab.1 Design index of digital IF system

|                | 参数值   |

|----------------|-------|

| 中频频段/GHz       | 2.6   |

| 带宽/MHz         | 40    |

| 动态范围(精度1dB)/dB | >66   |

| 工作模式           | FDD   |

| 调制方式           | QPSK  |

| 数据速率(max)/MSPS | 61.44 |

| 发射功率(max)/dBm  | 0     |

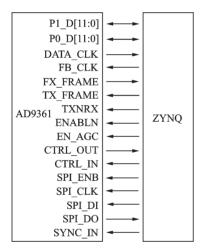

#### 2.3 数字接口设计

AD9361外部接口主要传输3种数据,控制数

图 6 同步控制电路

Fig.6 Synchronous control circuit

据、信号数据和状态数据。根据数据特点的不同, 本方案设计通过三种接口实现相关数据的传输。 其数据接口如图7所示。

图 7 AD9361与ZYNQ数据接口

Fig.7 Data interface between the AD9361 and ZYNQ

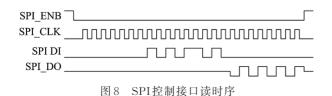

对于控制数据,具有多次读写的操作,但数据量很小,设计控制数据通过SPI接口进行相关寄存器的读写操作,采用传统四线模式进行数据的读写,通过SPI\_DI信号进行写入,SPI\_DO信号进行读取,当SPI\_ENB处于低电平时允许数据的传输。读时序如图8所示。

写入时序类似,但SPI\_DO在写入时保持低电平。对于信号数据,具有连续传输且高速传输的特

Fig.8 SPI control interface read timing

点,对于ZYNQ与AD9361之间的数据流的传输采用6位LVDS的方式以保证传输速率和可靠性。对于不同的工作模式,传输的数据格式不同,在单发单收模式下,采用FDD模式,时序设计如图9所示。

图 9 LVDS 数据接口接收时序 Fig. 9 LVDS data interface receive timing

而对于芯片的状态信息和控制则采用 GPIO 接口实现,通过高低电平的形式实现芯片工作状态的读取和控制。

#### 2.4 控制程序设计

数字中频系统的控制程序主要分为两个部分: 1)基于 ARM 的软件驱动; 2)基于 FPGA 的数字信号处理和接口。

软件驱动设计方式主要有两种:1)基于 Linux 系统的设计方式,通过操作系统实现相关功能,其优势在于界面清晰,控制方式简洁,但是 CPU 占用率较大;2)基于 no-OS 的设计方式,通过 SDK 软件进行设计。文中采用 no-OS 的方式。 ADI 和XILINX公司提供了大量不同器件的驱动库。软件设计中,仅需设计用户功能模块,再调用相关函数即可完成驱动。大部分工作是对硬件驱动程序进行配置,包括 SPI、UART、IIC等,主要修改相关接口匹配设备。

针对基带处理数据生成设计采用QPSK的调制 方式进行信号的调制,QPSK调制信号产生主要有 两种算法:1)四相位选择法,通过生成四种相位的载 波,根据IQ路电平信号进行载波的选择即可直接生成QPSK调制数据;2)调相法,IQ路01数据转换位十1/一1电平,分别与sin和cos载波相乘并相加也可得到调制数据。根据AD9361收发数据寄存器说明,PL侧需提供16位I路和Q路数据合并的32位数据,由于需要I路和Q路的数据,设计中选择第二种。

对于原始 0/1 数据, QPSK 通过电平转换将输入比特流转换为 +1/-1 数据流, 通过串并变换形成双路数据, 并乘以正弦和余弦载波。对于 IQ 路数据可表示为:

#### $I(t) = \pm \sin(\omega t)$

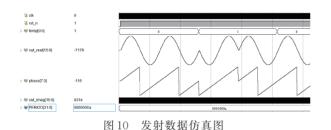

对于正弦信号,符号的变化相当于相位的变化,则只需要统计信号的相位再计算相应的正弦值即可。通常计算正弦值的算法有查找表法和坐标旋转计算机<sup>[7]</sup>(Coordinate Rotation Digital Computer,CORDIC)算法。查找表法实现高精度计算需要占用大量存储资源,这对于硬件部分是难以承受的,因此使用CORDIC算法来实现IQ路数据的计算。仿真结果如图10所示。

Fig.10 Simulation diagram of transmission data

为了验证硬件部分生成数据的可靠性,通过仿真对数据进行分析。如图 10 所示,图中 temp 为 0/1数据绝对码转换的相对码,out\_real 为 I 路信号数据,phase为 I 路信号相位。可见当 temp 为 1 时,信号发生翻转,符合 QPSK调制原理。

其次 PL 侧还需配置收发芯片相关的接口逻辑 以及数据的打包与解包,以保证数据按照要求的帧 格式进行传输。通过软件和硬件的分开设计,使得 软硬件功能之间的影响大大减小,软件部分仅需要 配置与外设的数据接口即可兼容相应的功能,灵活 性大大提高。

# 3 测试分析

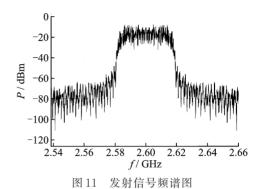

为了验证数字中频系统的可靠性,对发射通道进行测试。通过SDK设计软件功能配置系统PS部分,使用设计的QPSK硬件数据处理模块配置PL侧。收发芯片配置IP核将完成映射的32位基带信号数据流转换为6位差分信号通过LVDS协议传输至收发芯片,通过DAC采样后与设定的2.6 GHz发

射本振信号混频,形成频带信号后,设置最大发射功率。将信号通过发射口接入频谱仪测试分析。测试结果如图11所示。

Fig.11 Spectrum diagram of transmitted signal

AD9361芯片单音信号最大发射功率为0dBm, 载波信号最大发射功率为-7dBm,测试峰值为-7.3dBm,接近理论值,同时发射带宽满足40MHz的大带宽要求。

### 4 结束语

文中对大规模天线波束赋形架构进行了研究分析,提出了新型的混合波束赋形架构,并对波束预编码性能进行了仿真分析,满足系统较低复杂度、较好灵活性的需求;同时对宽带数字中频系统进行了研究设计,实现了四通道宽带收发数字中频系统。测试结果显示系统运行正确,满足指标要求。

#### 参考文献

- [1] 尤肖虎,潘志文,高西奇,等.5G移动通信发展趋势与若干关键 技术[J].中国科学:信息科学,2014,44(5):551-563.

- [2] 李伟斌,张学良,余炜平.基于混合波束赋形架构的射频系统方案设计[J].自动化与仪器仪表,2020(12):190-193,197.

- [3] Yu X, Shen J C, Zhang J, et al. Alternating minimization algorithms for hybrid precoding in millimeter wave MIMO systems [J]. IEEE Journal of Selected Topics in Signal Processing, 2016(10): 485-500.

- [4] 李光辉.基于码本的混合波束赋形技术研究[D].北京:北京邮电大学,2018.

- [5] Alkhateeb A, El Ayach O, Leus G, et al. Channel estimation and hybrid precoding for millimeter wave cellular systems [J]. IEEE Journal of Selected Topics in Signal Processing, 2014 (8): 831-846.

- [6] Huang H, Song Y, Yang J, et al. Deep-learning-based millimeter-wave massive MIMO for hybrid precoding [J]. IEEE Transactions on Vehicular Technology, 2019 (3): 3027-3032.

- [7] Kumar P A. FPGA implementation of the trigonometric functions using the CORDIC algorithm [C]. 2019 5th International Conference on Advanced Computing & Communication Systems (ICACCS), Coimbatore, India, 2019: 894-900.